PCI-SIG Finalizes and Releases PCIe 4.0, Version 1 Specification: 2x PCIe Bandwidth and More

by Nate Oh on October 26, 2017 1:00 PM EST

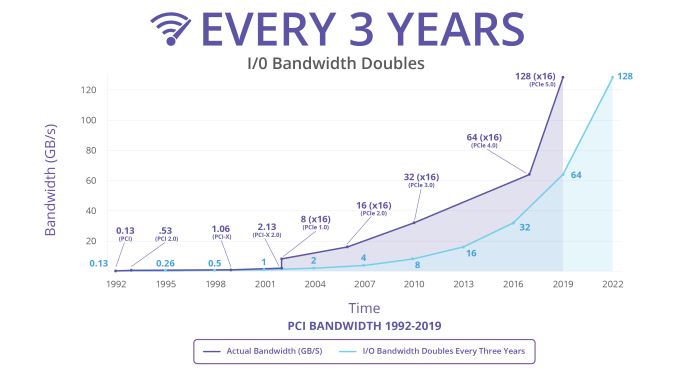

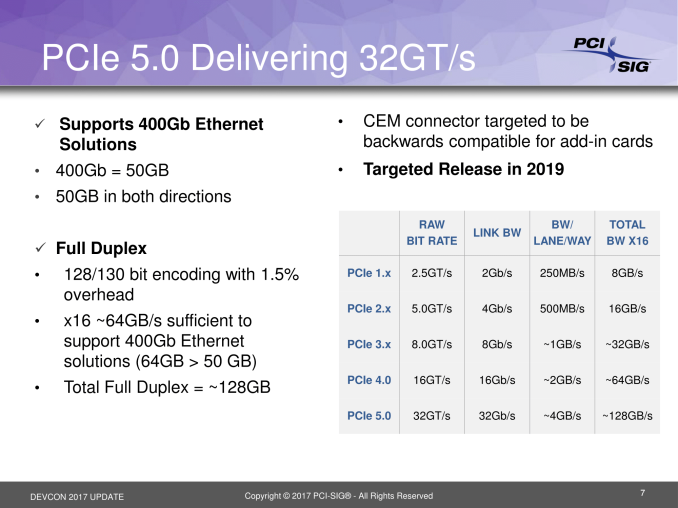

This week, PCI-standards consortium PCI-SIG (Special Interest Group) has ratified and released specifications for PCIe 4.0 Specification Version 1, uploading the documents to their PCI-SIG Specification Library. This marks the full release of PCIe 4.0, following up on June’s revision 0.9 specification publication. Doubling PCIe 3.0’s 8 GT/s (~1 GB/s) of bandwidth per lane, PCIe 4.0 offers a transfer rate of 16 GT/s with flexible lane width configurations, providing significant I/O performance benefits useful for storage, networking, and AI applications. At the same time, PCI-SIG has targeted Q2 2019 for releasing the finalized PCIe 5.0 specification, so PCIe 4.0 won't be quite as long-lived as PCIe 3.0 has been.

In context, PCI-SIG has previously kept to a four year cadence for PCIe 1.0 (2003), PCIe 2.0 (2006), and PCIe 3.0 (2010). In regards to the seven year delay, PCI-SIG noted that PCIe 3.0 provided sufficient bandwidth for some time before the developments and rising demands of AI compute workloads, PCIe NVMe and 3D XPoint storage, and networking speeds, particularly as 10GbE becomes more and more accessible to consumers. For compute GPUs, the bandwidth limitations of PCIe 3.0 had already driven NVIDIA in developing their proprietary NVLink interconnect. Consequently, with PCIe 4.0 and beyond, the PCI-SIG is looking to get back towards a more normal cadence, especially as they've now resolved some of the major technical hurdles in enabling faster transfer rates via the PCIe 4.0 standard.

The other aspect is the nature of the organization. PCI-SIG has almost 800 member companies, from which they annually elect a board of directors; for 2017-2018, the Board includes members from AMD, Intel, and NVIDIA. In developing and maintaining the open PCI specifications, members collaborate in committees and technical workgroups, submitting and reviewing specification changes. Part of PCI-SIG’s recent work is in streamlining in this process.

Once the specifications are finalized, members must have products pass interoperability and compliance tests at one of PCI-SIG’s many Compliance Workshops throughout the year, in order for the product to be added to the Integrators List, which OEMs and system integrators use in choosing hardware. For PCIe 4.0, PCI-SIG offered pre-publication Compliance Workshops for the first time, utilizing the earlier revision 0.9, but only at a preliminary “FYI Testing” level. For the rest of the year, PCI-SIG will offer PCIe 4.0 FYI Testing at Compliance Workshops; for the time being, PCIe 4.0 is not listed on either the official Compliance Program and Integrators List.

Like the previous PCIe iterations, PCIe 4.0 features backwards compatibility, and PCIe 1.x, 2.x, and 3.x cards will fit PCIe 4.0 slots and operate normally. PCIe 4.0 also maintains PCIe 3.0’s 128b/130b encoding, which will continue to be used in PCIe 5.0.

Among the other improvements, several features are more relevant for designers and developers than end users. As data rates increase, performance variation rises and signal integrity degrades. With that in mind, PCIe 4.0 brings lane margining at the PHY receiver, where the PCIe controller obtains electrical margin information of each PCIe lane in order to measure variation tolerance. PCIe 4.0 also has extended tags and credits, features that work together to mask latency and promote full bandwidth saturation. Other improvements include overall reduced system latency, I/O virtualization and platform integration, and added lanes/bandwitdth scalability, as well as enhanced Reliability, Availability, Serviceability (RAS) capabilities.

While gaming graphics cards are the most visible PCIe device to consumers, additional PCIe bandwidth overhead is unlikely to affect gaming performance, at least right away. However given the limited amount of PCIe bandwidth available with most consumer CPUs - just 16 general purpose lanes from the CPU with another 4 lanes for the chipset - this will also go a long way towards easing the pressure that the combination of GPUs, NVMe SSDs, and 10GigE networking can place on system I/O bandwidth. What may also be relevant is increased power capability from the secondary connectors, but at this point there are no further details, and a PCIe 4.0 Electromechanical Specification has not been disclosed.

As far as PCIe 4.0 vendor solutions go, Synopsys and Cadence, among others, are developing or offering 16GT/s PHYs and controllers, validation tools, and many other applications. IBM’s POWER9 feature PCIe 4.0 connections and Intel’s 10nm Falcon Mesa FPGA supports PCIe 4.0 as an IP block embedded via EMIB. Meanwhile, AMD have targeted 2020 for PCIe 4.0 support. But before products hit shelves, the PCIe 4.0 compliance and interoperability tests need to be finalized with both specifications and tools/procedures, and with the 32GT/s PCIe 5.0 fast-tracked to 2019, there may be very few, if any, consumer PCIe 4.0 devices. In any case, PCI-SIG only referred to the current PCIe 5.0 version 0.3, despite targeting Q4 2017 for version 0.5 at Hot Chips 2017.

PCI-SIG members may download the PCIe 4.0 specification for free at the Specification Library. Non-members may purchase a hard copy of the specification for $4,500.

Source: PCI-SIG

26 Comments

View All Comments

willis936 - Friday, October 27, 2017 - link

Heaven forbid that my next replacement machine is also an upgrade. Unless you mean that electronics should live forever.Sahrin - Friday, October 27, 2017 - link

Infinity Fabric 2.0 here we come!BubbaJoe TBoneMalone - Friday, October 27, 2017 - link

Does PCIe 5.0 have the bandwidth for 4k HDR10+ VR at 120fps?mkozakewich - Monday, October 30, 2017 - link

3840 x 2160 pixels x 30 bits/pixel x 120 fps = ~30 Gbps, which would be PCIe 5.0 1x or PCIe 3.0 4x. But then, we don't really connect these devices through PCIe. Meanwhile, transfer rate really doesn't mean much when discussing GPUs, so if you were talking about rendering the scene that's entirely different.skavi - Sunday, October 29, 2017 - link

I'm most hyped for Thunderbolt docks with less compromise.jimjamjamie - Wednesday, November 1, 2017 - link

I noticed in the AMD Carizzo review that the chip has 8 PCIe lanes citing power efficiency due to its mobile origins. If I've understood this article correctly PCIe 4.0 should be able to deliver the same bandwidth with half the lanes, so it sounds like we could see efficiency gains here.