Intel Updates ISA Manual: New Instructions for Alder Lake, also BF16 for Sapphire Rapids

by Dr. Ian Cutress on April 1, 2020 5:00 AM EST- Posted in

- CPUs

- Intel

- TSX

- Security

- Sapphire Rapids

- Alder Lake

- Instructions

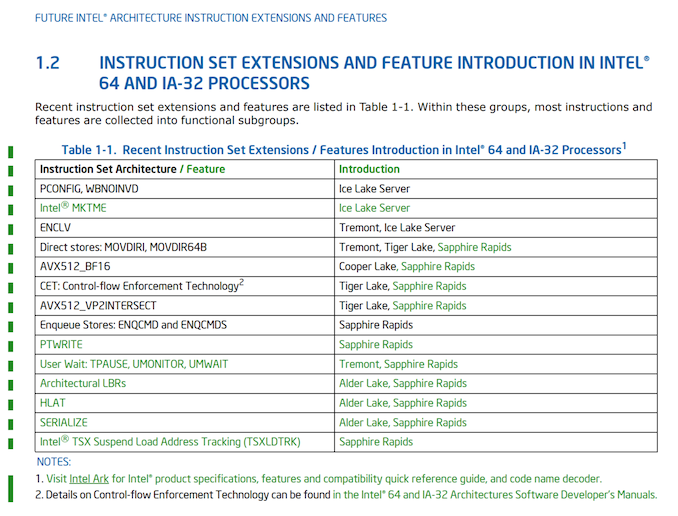

As with any processor vendor, having a detailed list of what the processor does and how to optimize for it is important. Helping programmers also plan for what’s coming is also vital. To that end, we often get glimpses of what is coming in future products by keeping track of these updates. Not only does it give detail on the new instructions, but it often verifies code names for products that haven’t ‘officially’ been recognized. Intel’s latest update to its ISA Extensions Reference manual does just this, confirming Alder Lake as a future product, and identifies what new instructions are coming in future platforms. Perhaps the biggest news of this is actually the continuation of BFLOAT16 support, originally supposed to be Cooper Lake only (and bearing in mind, Cooper Lake will have a limited launch), but will now also be included in the upcoming Sapphire Rapids generation, set for deployment in the Aurora supercomputer in late 2021.

In the 38th Edition of the ISA Extensions Reference manual from Intel, the company has a table front and center with all the latest updates an instructions coming to future platforms. From this, we can plot what platforms will be getting which instructions.

| Intel Instruction Support | ||||||

| AnandTech | Tremont Atom |

CPR Xeon |

ICL Xeon |

SPR Xeon |

Tiger Lake |

Alder Lake |

| PCONFIG | ✓ | ? | ||||

| WBNOINVD | ✓ | ? | ||||

| Intel MKTME | ✓ | ? | ||||

| ENCLV | ✓ | ✓ | ? | |||

| MOVDIR* | ✓ | ✓ | ✓ | ? | ||

| AVX512_BF16 | ✓ | no | ✓ | |||

| AVX512_VP2INTERSECT | ✓ | ✓ | ? | |||

| CET | ✓ | ✓ | ? | |||

| ENQCMD* | ✓ | |||||

| PTWRITE | ✓ | |||||

| TPAUSE, UM* | ✓ | ✓ | ||||

| Arch LBRs | ✓ | ✓ | ||||

| HLAT | ✓ | ✓ | ||||

| SERIALIZE | ✓ | ✓ | ||||

| TSXLDTRK | ✓ | |||||

Starting with what I think is big news: BF16 support in Sapphire Rapids. It is clear from this manual that BF16 will not be supported in Ice Lake Server, which means that technically BF16 will skip a generation, going from Cooper Lake to Sapphire Rapids. But as we’ve reported on previously, Cooper Lake has changed from a wide launch for everyone to a minimal launch for select customers only, and those that focus on 4S and 8S topologies (like Facebook). So this could be considered more of a ‘delayed’ launch, assuming Sapphire Rapids is going to be widely used. Anyone planning to use Cooper Lake for BF16 compatible workloads will have to wait an extra couple of years.

The other big news is the mentioning of Alder Lake. Up until this point, Alder Lake has only been mentioned in unconfirmed slides, or LinkedIn profiles of engineers who have worked on it (and subsequently those references were removed). As far as we understand, Alder Lake is the 10nm product following on from Tiger Lake. Tiger Lake (what we know so far) is a quad-core mobile chip due for launch at the end of 2020, which means Alder Lake is likely to be at the tail end of 2021.

What Alder Lake (and Sapphire Rapids) gets for instructions includes Architectural LBRs (Last Branch Recording) in order to speed up branches, HLAT (Hypervisor-managed Linear Address Translation), which forces linear address translation, and SERIALIZE, which forces a command to go through a core with all the caches pre-flushed and waits for all buffered writes to have finished before starting. The LBR update helps with performance, the HLAT is primarily for Sapphire Rapids, and the SERIALIZE is to assist with recent security issues.

Also of note are some of the Ice Lake Server updates. It now lists Ice Lake Server as getting Intel’s MKTME, Intel’s Multi-Key Total Memory Encryption, which are a set of memory encryption techniques for multiple encrypted environments, increasing the scope of these technologies with a key to matching/surpassing AMD’s prowess in this area. The other one to note (but not new for this document) is ENCLV support, which SGX related to secure enclaves.

Another point of security is the new TSXLDTRK instruction for Sapphire Rapids. This is a TSX Load Tracking ‘suspend’ instruction, with a corresponding XRESLDTRK to resume load tracking for TSX. (TSX = Transactional Memory.)

The full information about these new instructions can be found on Intel’s Developer Zone.

Source: Instlatx64 on Twitter

Related Reading

- I Ran Off with Intel’s Tiger Lake Wafer. Who Wants a Die Shot?

- Intel’s Cooper Lake Plans: The Chip That Wasn’t Meant to Exist, Fades Away

- Intel to Offer Socketed 56-core Cooper Lake Xeon Scalable in new Socket Compatible with Ice Lake

- Intel Architecture Manual Updates: bfloat16 for Cooper Lake Xeon Scalable Only?

- Cisco Documents Shed Light on Cascade Lake, Cooper Lake, and Ice Lake for Servers

- An Interview with Lisa Spelman, VP of Intel’s DCG: Discussing Cooper Lake and Smeltdown

- Intel at CES 2020: 45W 10th Gen Mobile CPUs Soon, Tiger Lake with Xe Graphics Later

- Intel’s Confusing Messaging: Is Comet Lake Better Than Ice Lake?

34 Comments

View All Comments

soresu - Wednesday, April 1, 2020 - link

Wow, they really didnt learn their lesson from the AVX512 fragmentation mess at all.ksec - Wednesday, April 1, 2020 - link

Exactly, I think what Intel is trying to do is keeping Cooper Lake for 4S/ 8S, while Icelake for 1S and 2S without BFLOAT16.This is just another sign they are rushing ahead to 7nm. But then Alder Lake is 10nm++. So there wont be Intel 7nm in Laptop Chip even in 2022?

Santoval - Thursday, April 2, 2020 - link

Tiger Lake will be released with up to 6 cores for the -H version (45W). Strangely it will be also be fabbed at 10nm+, the same as Ice Lake, so I am not sure what kind of "transistor optimizations" it could have since it's the same node variant (unless Intel calls the node of Ice Lake "10nm", pretending that Cannon Lake and the beta 10nm-- node it was fabbed on never existed).Since Alder Lake will be fabbed on 10nm++ perhaps they will manage to reach up to 8 cores, though still for up to -H parts; presumably with up to 6 cores for -U parts. So yes, 2022 will be the year of Alder Lake laptops - assuming minimal delays. Since Alder Lake will sport Golden Cove cores its 7nm successor that will be released in 2023 (at the *absolute* earliest), tentatively called "Meteor Lake" as of today, should sport Ocean Cove cores. That's the μarch Jim Keller and his team have been developing for a few years now, which is said to be Intel's *true* next-gen μarch (Intel's Zen equivalent).

Deicidium369 - Tuesday, April 28, 2020 - link

New architecture (Sunny Cove / Willow Cove) as well as a new process. Look at the most current 14nm and the very first 14nm... quite different.Cannon Lake was 10nm-, the 2.7x density was too aggressive - so 10nm is 2x density and 10nm+ is the 2.7x density increases. Tiger Lake is 10nm+ and would think that ICL Xeon would be as well.

Skylake is Intel's Zen equiv.

ashleysguy43 - Sunday, April 5, 2020 - link

Sara Jackson Makes $140 to $180 per day online work and i received $16894 in one month online acting from home.I am a daily student and work simply one to a pair of hours in my spare time.Everybody will do that job and monline akes extra cash by simply open this link... WWW.iⅭash68.ⅭOⅯDeicidium369 - Tuesday, April 28, 2020 - link

2 completely different markets. Most hyperscalers are interested in bfloat16 and the high socket count - so makes sense. The people buying Ice Lake Xeons are going to be replacing 2 socket with 2 socket.2022 is the general launch date for that node - 1st will be Xe HPC (Ponte Vecchio) and Sapphire Rapids (Xeon) - I am sure there will be a 7nm laptop SOC - but I doubt it will be in the initial 7nm launch.

mode_13h - Wednesday, April 1, 2020 - link

Well, if the main use case for BFloat16 is training, then you're not going to have people doing a lot of training on their laptop CPUs.It'd be great to have all instructions everywhere, but when you're talking about 512-bit, some of those extensions eat a lot of die space.

CityBlue - Wednesday, April 1, 2020 - link

Performance fixes. Security fixes. It's all lipstick on a pig.Does anyone have any faith/trust in SGX or TSX after the various security debacles? Can Intel really be trusted with total memory encryption given their track record with, you know, security vulnerabilities and system crippling exploits?

Intel need to go back to the drawing board and start from scratch, eliminating all the security shortcuts they took in their misguided quest for speed. Tacking on new instructions to work around their defective and compromised microarch isn't going to cut it.

Why wait 2 years for "new" (basically tweaked) hardware from Intel that only papers over the cracks when you can instead buy the competition today with more performance, fewer security worries and significantly cheaper. Win, win, win.

azfacea - Wednesday, April 1, 2020 - link

What good is a new instruction, if your products exist only in slidesJayNor - Wednesday, April 1, 2020 - link

I've seen the TPAUSE, UMONITOR, and MOVDIR instructions associated with fast accelerator accesses in a Tremont description. Interesting that they appear in Sapphire Rapids.Were any of the new instructions associated with the CXL operations?