Intel Launches Cooper Lake: 3rd Generation Xeon Scalable for 4P/8P Servers

by Dr. Ian Cutress on June 18, 2020 9:00 AM EST

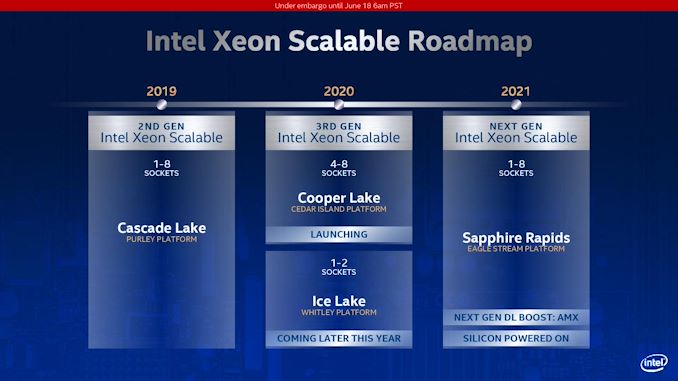

We’ve known about Intel’s Cooper Lake platform for a number of quarters. What was initially planned, as far as we understand, as a custom silicon variant of Cascade Lake for its high-profile customers, it was subsequently productized and aimed to be inserted into a delay in Intel’s roadmap caused by the development of 10nm for Xeon. Set to be a full range update to the product stack, in the last quarter, Intel declared that its Cooper Lake platform would end up solely in the hands of its priority customers, only as a quad-socket or higher platform. Today, Intel launches Cooper Lake, and confirms that Ice Lake is set to come out later this year, aimed at the 1P/2P markets.

Count Your Coopers: BFloat16 Support

Cooper Lake Xeon Scalable is officially designated as Intel’s 3rd Generation of Xeon Scalable for high-socket count servers. Ice Lake Xeon Scalable, when it launches later this year, will also be called 3rd Generation of Xeon Scalable, except for low core count servers.

For Cooper Lake, Intel has made three key additions to the platform. First is the addition of AVX512-based BF16 instructions, allowing users to take advantage of the BF16 number format. A number of key AI workloads, typically done in FP32 or FP16, can now be performed in BF16 to get almost the same throughput as FP16 for almost the same range of FP32. Facebook made a big deal about BF16 in its presentation last year at Hot Chips, where it forms a critical part of its Zion platform. At the time the presentation was made, there was no CPU on the market that supported BF16, which led to this amusing exchange at the conference:

BF16 (bfloat16) is a way of encoding a number in binary that attempts to take advantage of the range of a 32-bit number, but in a 16-bit format such that double the compute can be packed into the same number of bits. The simple table looks a bit like this:

| Data Type Representations | ||||||

| Type | Bits | Exponent | Fraction | Precision | Range | Speed |

| float32 | 32 | 8 | 23 | High | High | Slow |

| float16 | 16 | 5 | 10 | Low | Low | 2x Fast |

| bfloat16 | 16 | 8 | 7 | Lower | High | 2x Fast |

By using BF16 numbers rather than FP32 numbers, it would also mean that memory bandwidth requirements as well as system-to-system network requirements could be halved. On the scale of a Facebook, or an Amazon, or a Tencent, this would appeal to them. At the time of the presentation at Hot Chips last year, Facebook confirmed that it already had silicon working on its datasets.

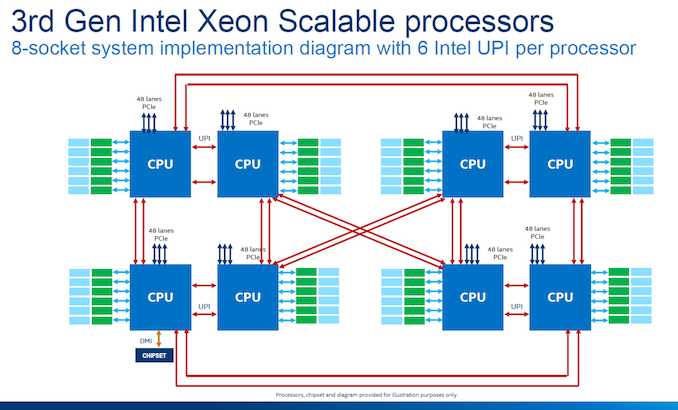

Doubling Socket-to-Socket Interconnect Bandwidth

The second upgrade that Intel has made to Cooper Lake over Cascade Lake is in socket-to-socket interconnect. Traditionally Intel’s Xeon processors have relied on a form of QPI/UPI (Ultra Path Interconnect) in order to connect multiple CPUs together to act as one system. In Cascade Lake Xeon Scalable, the top end processors each had three UPI links running at 10.4 GT/s. For Cooper Lake, we have six UPI links also running at 10.4 GT/s, however these links still only have three controllers behind them such that each CPU can only connect to three other CPUs, but the bandwidth can be doubled.

This means that in Cooper Lake, each CPU-to-CPU connection involves two UPI links, each running at 10.4 GT/s, for a total of 20.8 GT/s. Because the number of links is doubled, rather than an evolution of the standard, there are no power efficiency improvements beyond anything Intel has done to the manufacturing process. Note that double the bandwidth between sockets is still a good thing, even if latency and power per bit is still the same.

Intel still uses the double pinwheel topology for its eight socket designs, ensuring at max two hops to any required processor in the set. Eight socket is the limit with a glueless network – we have already seen companies like Microsoft build servers with 32 sockets using additional glue logic.

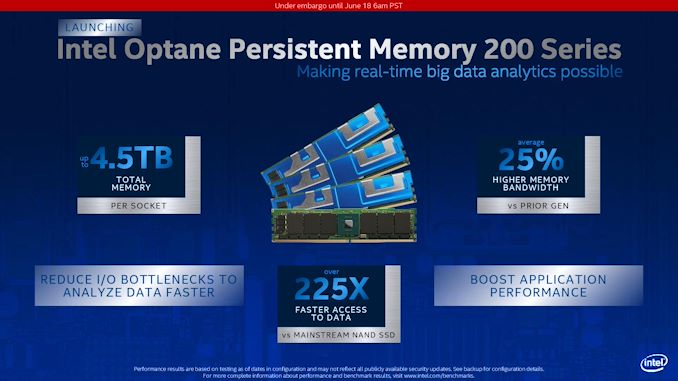

Memory and 2nd Gen Optane

The third upgrade for Cooper Lake is the memory support. Intel is now supporting DDR4-3200 with the Cooper Xeon Platinum parts, however only in a 1 DIMM per channel (1 DPC) scenario. 2 DPC is supported, but only at DDR4-2933. Support for DDR4-3200 technically gives the system a boost from 23.46 GB/s per channel to 25.60 GB/s, an increase of 9.1%.

The base models of Cooper Lake will also be updated to support 1.125 TiB of memory, up from 1 TB. This allows for a 12 DIMM scenario where six modules are 64 GB and six modules are 128 GB. One of the complaints about Cascade Xeons was that in 1 TB mode, it would not allow for an even capacity per memory channel when it was filled with memory, so Intel have rectified this situation. In this scenario, it means that the six 128 GB modules could also be Optane. Why Intel didn’t go for the full 12 * 128 GB scenario, we’ll never know.

The higher memory capacity processors will support 4.5 TB of memory, and be listed as ‘HL’ processors.

Cooper Lake will also support Intel’s second generation 200-series Optane DC Persistent Memory, codenamed Barlow Pass. 200-series Optane DCPMM will still available in 128 GB, 256 GB, and 512 GB modules, same as the first generation, and will also run at the same DDR4-2666 memory speed. Intel claims that this new generation of Optane offers 25% higher memory bandwidth than the previous generation, which we assume comes down to a new generation of Optane controller on the memory and software optimization at the system level.

Intel states that the 25% performance increase is when they compare 1st gen Optane DCPMM to 2nd gen Optane DCPMM at 15 W, both operating at DDR4-2666. Note that the first-gen could operate in different power modes, from 12 W up to 18 W. We asked Intel if the second generation was the same, and they stated that 15 W is the maximum power mode offered in the new generation.

99 Comments

View All Comments

Deicidium369 - Thursday, June 18, 2020 - link

Not in the case of BFloat they don't. Stick to desktops.AlexDaum - Friday, June 19, 2020 - link

AVX-512 is great for performance, but it requires good programmers to make use of it, since it is no easy task creating an AVX optimised codepath.Deicidium369 - Saturday, June 20, 2020 - link

All programming needs good programmers... most of the organizations that will have a use for ZVX will be able to draw upto existing libraries to integrate into a custom program...eek2121 - Thursday, June 18, 2020 - link

It will be interesting if Milan supports bfloat16 as well. Unless AMD segregates enterprise chips (they will at some point), it would mean that bfloat16 trickles down to desktop chips.Deicidium369 - Saturday, June 20, 2020 - link

Well Intel comes out with a feature, and then AMD copies it - so pretty sure bfloat is coming to AMD and AVX-512...Spunjji - Friday, June 19, 2020 - link

There's no such thing as a "low priced" 4S Xeon system, though. The processors are expensive and so are the servers you put them into.That's been AMD's pitch the whole time - consolidate more cores into fewer sockets for a lower cost of ownership. If you want to do DL/ML you put in accelerators for those jobs, which again, will be cheaper than trying to reach the same performance with a Xeon.

Intel are trying to find niches for their CPUs to occupy, but those niches are better occupied by products that cater to them specifically.

Deicidium369 - Saturday, June 20, 2020 - link

most of Cooper Lake will be for hyper scalers - not just, but most.Deicidium369 - Thursday, June 18, 2020 - link

Smokes them in number shipped, market adoption, market share and revenues. From a business standpoint that is all that mattersschujj07 - Thursday, June 18, 2020 - link

That seems to be the only retort that you ever have for Intel. What you fail to realize is that given time those numbers will change if Intel continues to falter. Ice Lake is very late and when it comes out will be competing against 3rd Gen Epyc. We already know from laptops that Zen 2 competes quite well with Ice Lake on a performance side. We also know that Ice Lake has had frequency problems and has high power draw relative to Zen 2. Those things don't bode well for it in the data center. We already are seeing more companies moving to Epyc, especially those that have CTOs/CIOs that don't follow the Intel only mantra. In the enterprise world the tables are turning for Intel, much the same way it did for IBM years ago. It used to be that "no one was ever fired for buying IBM" now it is "no one was ever fired for buying Intel." That first statement eventually died and was replaced by the 2nd, and the 2nd is starting to die as well.AlexDaum - Friday, June 19, 2020 - link

The main advantage of the Intel Xeons over Epyc is AVX-512 Support, which can have a large performance impact in some Software that can make use of it