Intel to Create RISC-V Development Platform with SiFive P550 Cores on 7nm in 2022

by Dr. Ian Cutress on June 22, 2021 9:01 AM EST

As part of SiFive’s announcements today, along with enabling SiFive IP on Intel’s Foundry Service offerings, Intel will be creating its own RISC-V development platform using its 7nm process technology. This platform, called Horse Creek, will feature several of SiFive’s new Performance P550 cores also being announced today, and will be paired with Intel’s DDR and PCIe IP technology.

On first reading into the press release, it isn’t 100% clear that Intel’s commentary discusses a platform with P550 as a host or as an add-in device: to quote Intel, ‘We are pleased to be a lead development partner with SiFive to showcase to mutual customers the impressive performance of their P550 on our 7nm Horse Creek platform’. Intel historically typically keeps its Creek family names, such as Boulder Creek, Cherry Creek, or Timber Creek, for socketed platforms - not for all-in-one embedded development platforms. Not only that, the wording makes it sound like we should consider a RISC-V core as an assistant core managing another part of a system.

However it would appear that Intel intends to make this a fully-featured development system, along similar lines to SiFive’s own HiFive Unmatched platform launched early this year. What makes this special is that Intel is committing to developing the SoC on its own 7nm process node, which provides a ‘simpler’ vehicle for Intel to test and ramp up its 7nm technology. This can be coupled with increasing interest in RISC-V development, and deploying a platform though Intel’s supply chain and distribution might have a far reach to put these in the hands of upcoming developers.

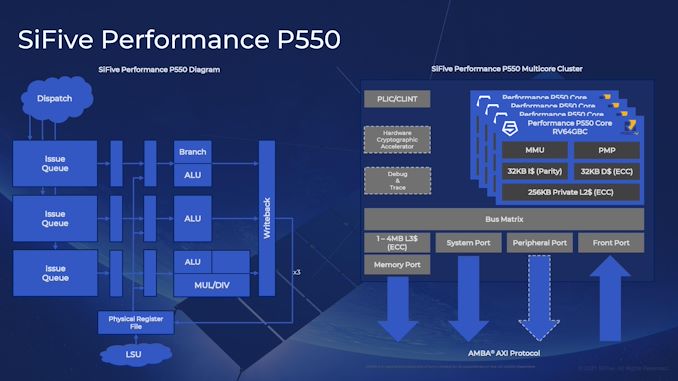

The new SiFive Performance P550 core at the heart of Horse Creek is SiFive’s highest performance processor to date, with the company quoting a SPEC2006int of 8.65 per GHz. It is a Linux-capable core, with full support for the RISC-V vector extension v1.0rc. It has a 13-stage triple-issue out-of-order microarchitecture with a private 32KB+32KB L1 cache and a private L2 cache (per core) The design supports four cores in a single cluster that can be paired up to 4 MB of shared L3.

The time scale for this platform coming to market is quite interesting. Despite Intel recently committed to bringing its 7nm to market in 2023 with the compute tile for its Meteor Lake processor as its first 7nm product, we’re being told that Horse Creek silicon will be ready in 2022, which would make Horse Creek its first 7nm product. For what it is worth, it’s unlikely that the Intel RISC-V solution is tile-based, but it might be easy enough to bring a small RISC-V chip development platform to market around then. The chip is likely to be small, so that might work in favor of its costs as well. A question does remain as to whether Intel’s involvement here is purely in the hardware, or whether there will be an Intel-based software stack to go along with it.

Related Reading

- Samsung to Use SiFive RISC-V Cores for SoCs, Automotive, 5G Applications

- SiFive Announces First RISC-V OoO CPU Core: The U8-Series Processor IP

- SiFive Acquires USB 2.0 and 3.x IP Portfolio to Strengthen RISC-V SoCs

- SiFive Unveils Freedom Platforms for RISC-V-Based Semi-Custom Chips

- Western Digital’s RISC-V "SweRV" Core Design Released For Free

35 Comments

View All Comments

MetalPenguin - Monday, June 28, 2021 - link

If things are designed correctly, a 64-bit SIMD floating point pipeline won't have a ton of overhead compared to just a floating point pipeline which supports double precision. The bulk of the arithmetic hardware can be shared between different precisions. But I agree that adding support for SIMD integer or the other instructions which A75 supports would increase the area for U84.Another thing is that "3 times faster" cannot be applied universally to all workloads. For a high-ILP workload that always hits out of the caches, U84 may only be something like 50% faster (3 integer pipes vs. 2 for example) or less. But for something which incurs DCache misses, the U84 can run laps around the U74.

Anyway, I'm looking forward to getting real silicon measurements from the P550 eventually.

Wilco1 - Tuesday, June 29, 2021 - link

Me too, but it looks like it's going to a very long wait... There are no measurements for U84 yet almost 2 years after being announced. There is only a recent Geekbench result for U74 at 1.0GHz: https://browser.geekbench.com/v5/cpu/8493132The fun thing is SiFive likes to call U74 a Cortex-A55 equivalent when in reality it gets about half the performance of Cortex-A53 (eg. Pi 3 B at 1.2GHz: https://browser.geekbench.com/v5/cpu/8201396 )

mode_13h - Monday, June 28, 2021 - link

> Just two 64-bit NEON/FP pipes I believe. The P550 also has 64-bit FP supportThere's a big difference between a 64-bit FP pipe and a 64-bit SIMD pipe, once you go to smaller data types, such as those used in deep learning.

Wilco1 - Tuesday, June 29, 2021 - link

Agreed. Neon adds hundreds of instructions, so it's big increase in decode, double the FP register file, lots of new ALUs as you can't do integer arithmetic on an FP pipe etc. And RISC-V does add something similar to SVE which is even more complex with gather/scatter, predicates etc. Lots more complexity, lots more instructions = lots more transistors.mode_13h - Wednesday, June 30, 2021 - link

> Lots more complexity, lots more instructions = lots more transistors.Hey, I never said it was free!

: )

I was just reacting to the way MetalPenguin seemed to be almost equating a 64-bit NEON pipe almost to a 64-bit FP pipe. BIG difference!