MIPS Strikes Back: 64-bit Warrior I6400 Arrives

by Stephen Barrett on September 2, 2014 10:00 AM EST

Introduction

One of ARM’s most tangible business advantages is its offer of both CPUs and GPUs to SoC designers. Anyone with experience in business to business relationships knows just how complex forming and maintaining a mutually beneficial collaboration can be. Setting up contracts, forming rapport, defining goals, and even just understanding documentation and technical content formatting all takes time. Unless there is significant benefit to investing in two different relationships and technologies, it is simpler (read: cheaper) to single source contributing components of a design. There are down sides of single sourcing (see Boeing 787 battery fiasco), but depending on a business’ capacity for risk, the savings are undeniable. Especially when ARM undoubtedly offers bundle pricing promotions.

When Imagination Technologies acquired MIPS Technologies in 2012 for $100 million, their goal was very clear – attack ARM. Imagination’s GPU business was already wildly successful, with design wins in a bevy of high end mobile devices including those from Samsung and Apple. Adding the CPU cores from MIPS, with their decades of history designing and licensing IP, strategically positioned Imagination opposite ARM’s licensing business. Imagination’s executives have also stated they are prepared to offer aggressive IP bundling discounts.

Looking at Imagination’s product, press, demos, and interviews, it appears they are not (yet?) positioning MIPS cores to combat ARM cores at the high end of the market. Rather, they appear focused on being a viable alternative to ARM in multi-threaded and low power workloads. In fact, the vast majority of MIPS cores are currently used in network infrastructure where threading and power efficiency are paramount.

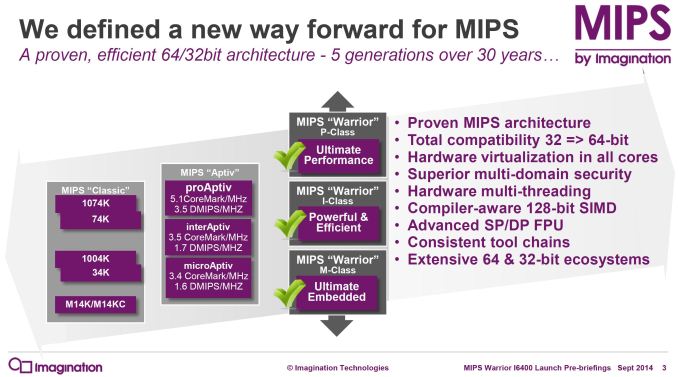

Today MIPS is announcing a major launch: the Warrior I6400 core. Based on the 64-bit MIPS64 instruction set (release 6), the Warrior I6400 core is the middle-class CPU core in a family of three, each targeting a different point in the power/performance curve. Imagination is releasing the I6400 core last, which is at the middle of the pack balancing performance with power. Imagination has already released their high-end P56xx series and low-end M51xx series.

The most analogous ARM core to the I6400 appears to be the ARM Cortex-A53, but I6400 has some interesting features we haven’t seen in this market before and MIPS estimates it will deliver higher performance. I’ve produced a table here to help put performance in context. Note that only A57, A53, P5600, and I6400 are 64-bit processors.

| MIPS and ARM High End IP Cores in Order of Performance | ||

| MIPS |

Manufacturer Estimated DMIPS/MHz/core |

ARM |

| 5.0 | Cortex-A57 | |

| 4.0 |

Cortex-A17 Cortex-A15 |

|

| P5600 | 3.5 | |

| I6400 | 3.0 | |

| 2.5 | Cortex-A9 | |

| 2.3 | Cortex-A53 | |

| 1.9 | Cortex-A7 | |

Keep in mind that these processors use different instruction sets (ISAs) so DMIPS are not directly comparable. However, as they are both RISC processors, the DMIPS should hopefully be roughly comparable. I would like to use directly comparable CoreMark scores but only MIPS provides CoreMark numbers for their processors.

While no one can accurately predict if Imagination will grab additional market share away from ARM, we can educate ourselves on this alternative before it potentially arrives in our hands and homes. And besides, competition is always a good thing.

84 Comments

View All Comments

alexvoica - Wednesday, September 3, 2014 - link

CoreMark is a superior benchmark over DMIPS and reflects real world performance and workloads - not all, I agree but it still covers a lot more. If you look at our CoreMark results, you will notice we use gcc.https://www.eembc.org/coremark/

not proprietary (and expensive) compilers. I recommend you actually click on the link, see for yourself and then come back here and copy/paste what it says in the compiler section of that page.

Again, if you had read my article and the press release, you would have seen we actually have said that we lead in SPECint scores AND provide better performance when using multithreading.

I have no problem talking to you or anyone here trying to dispute our claims but let's keep it civilized and not imply I am deliberately lying.

bji - Wednesday, September 3, 2014 - link

Why are you so hostile? Calm the freak down man.Wilco1 - Tuesday, September 2, 2014 - link

SPEC has a multithreaded variant called SPECrate, this runs as many threads as you want. Various compilers (eg. icc) do autoparallelize some of the SPEC benchmarks even for the base results. This has made SPEC almost useless as a single-threaded comparison. So what people do is ignore Intel's icc results and rerun SPEC using GCC with identical options on the CPUs to be compared.Samus - Wednesday, September 3, 2014 - link

Wow name99 and Wilco1 chill the fuck out you're way over-complicating this article. When we have working devices we'll get the real benchmark comparisons to the "ARM equivalent" but its well understood MIPS has superior performance per watt capability at the cost of code and compiler complexity, in the same way ARM has superior performance per watt over x86 at the cost of x86 compatibility. The legacy P55C datapath inherently inflats the transistor count and inefficiency of x86 CPU's, and this is starting to become an issue for ARM as they have over 15 generations of designs, most of which are all backwards compatible with each other.MIPS has just 6 generations of designs to contend with, and was already a more efficient processing method from the get go. ARM's initially superior licensing model and incredibly successful development platform are what has lead to their success decades later.

Wilco1 - Wednesday, September 3, 2014 - link

When we have working devices we can compare performance per Watt. Until then which will be more efficient is just a guess. MIPS and ARM started around the same time and have similar baggage accumulated. Note MIPS is a simpler ISA and actually easier for the compiler as it doesn't have some of the more complex instructions that ARM has.Samus - Wednesday, September 3, 2014 - link

MIPSv6 is way more complex than ARM57, just like MIPSv1 was way more complex than ARM4JAVA is JAVA, but the compiler and instruction sets are more advanced in MIPS, hence more complex. An author may chose not to use a lot of extensions, but long story short, I work with programmers all the time and optimizing for MIPS is more work as optimizing for ARM. There are a lot of reasons for this (admittedly, industry support being one huge one.)

Wilco1 - Wednesday, September 3, 2014 - link

Cortex-A57 is ARM's highest performance and most complex OoO core. You can't compare that with MIPSv6 - an architecture. Wait until Imagination designs a CPU with comparable performance.MIPS is a simpler ISA than ARM, so compilers are easier to write. But MIPS pays for that by having to use more instructions to achieve the same task and more complex hardware to achieve the same performance. The fusing of 2 loads or stores is a very good example of this - if this was supported in the ISA like on ARM, it wouldn't need to be special cased. And while it improves performance, you still pay with larger codesize.

defiler99 - Thursday, September 4, 2014 - link

MIPS is hardly the "new kid on the block"; the MIPS instruction set has always been a rare example of beauty and simplicity in design.It's hardly fair to call that article "marketing fluff" either; have you seen some examples of true fluff? That isn't one.

puppies - Tuesday, September 2, 2014 - link

The time to admit your affiliation was before you started your first post, not after you got called out on it......alexvoica - Tuesday, September 2, 2014 - link

Called out for using my real name and claiming ownership (I, my) of the article from the first post? Don't think so.