Skylake CPU Package: Mini-Analysis

by Ian Cutress on August 10, 2015 6:00 AM EST

As a short side piece from our in depth review on Intel's 6th Generation Core processors, codename Skylake, the well-known overclocker Splave has posted some very interesting images on the processor itself. We confirmed we are free to use the pictures below from him.

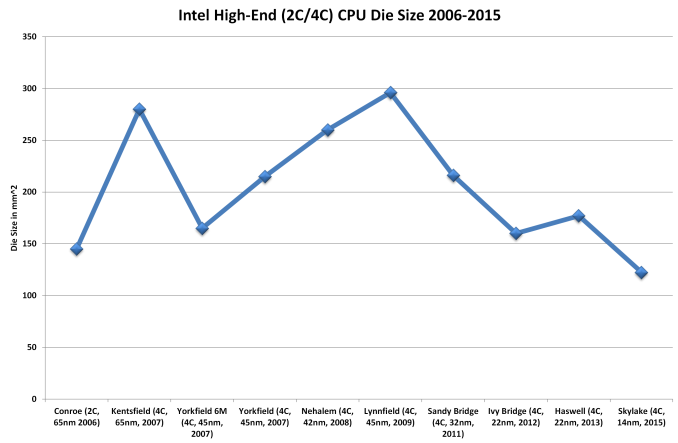

First up is an image of the Skylake i7 silicon die on package. With our trusty interpolation measuring skills, the die area for the GT2 enabled quad core system comes out at 9.05 mm by 13.52 mm, or 122.4 square mm. Let's put this into perspective with other dies:

| CPU Specification Comparison | |||||

| CPU | Process Node |

Cores | GPU | Transistor Count (Schematic) |

Die Size |

| Intel Skylake GT2 4C | 14nm | 4 | GT2 | ? | 122.4mm2 |

| Intel Broadwell-H GT3e 4C | 14nm | 4 | GT3e | ? | ? |

| Intel Haswell-E 8C | 22nm | 8 | N/A | 2.6B | 356mm2 |

| Intel Haswell GT2 4C | 22nm | 4 | GT2 | 1.4B | 177mm2 |

| Intel Haswell ULT GT3 2C | 22nm | 2 | GT3 | 1.3B | 181mm2 |

| Intel Ivy Bridge-E 6C | 22nm | 6 | N/A | 1.86B | 257mm2 |

| Intel Ivy Bridge 4C | 22nm | 4 | GT2 | 1.2B | 160mm2 |

| Intel Sandy Bridge-E 6C | 32nm | 6 | N/A | 2.27B | 435mm2 |

| Intel Sandy Bridge 4C | 32nm | 4 | GT2 | 995M | 216mm2 |

| Intel Lynnfield 4C | 45nm | 4 | N/A | 774M | 296mm2 |

| AMD Trinity 4C | 32nm | 4 | 7660D | 1.303B | 246mm2 |

| AMD Vishera 8C | 32nm | 8 | N/A | 1.2B | 315mm2 |

This makes Skylake the smallest die size for a quad core desktop processor from Intel we have seen, and that is including the integrated graphics in that calcualtion. Depending on the exact architectural details, previously in Haswell the die area was a near even split for cores and graphics after the L3 cache and IO functions (PCIe, Memory, DMI) were removed.

We won't know exact transistor numbers until they are disclosed at Intel's Developer Forum in mid-August, as well as a false color image die shot to show how much die area the main parts of the architecture are using. Although given the similarity to Haswell in terms of feature set (it seems to be similar with a few minor additions such as fixed function units, slightly different libraries, dual memory channels, DMI 3.0, etc.), if we take the number of transistors that GT2 Haswell had (1.4 billion) and put them in the die area we measure from the image, this comes out to a 11.4 million transistors per mm2.

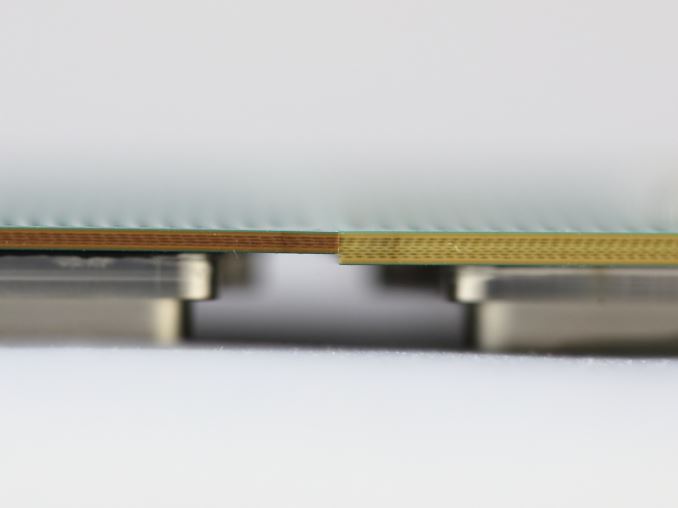

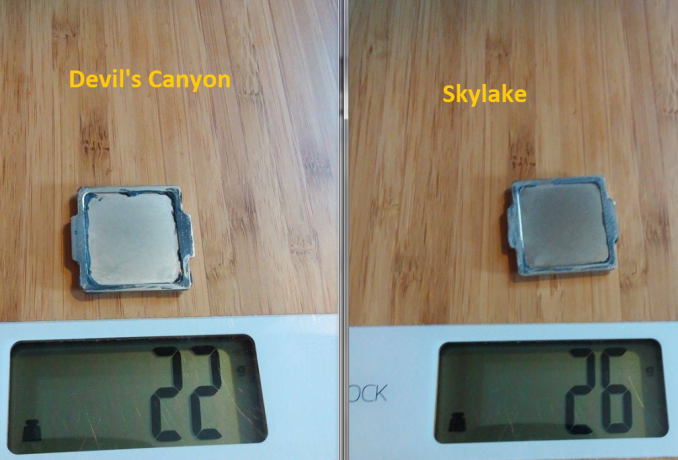

Die size aside, Skylake also has a substantially thinner package than Devil's Canyon:

According to PCWatch, the package thickness of the Core i7-4770K is 1.1mm, compared to 0.8mm for Skylake. This is a direct result of using fewer PCB layers, and here we count five for Skylake and eight for Haswell.

There could be several reasons for this. The removal of the fully integrated voltage regulator (FIVR) might reduce the number of PCB layers for power planes. The nature of the 14nm die might facilitate a thinner package as well. The cynical answer is that it is used to drive down cost. In the motherboard industry, a PCB with more layers is substantially more expensive but simplifies design when there are more features - there's also a side argument if more layers or fewer layers is better for overclocking. If we transplant this thinking to the processor, it becomes a balance of cost vs. complexity. Either way, the retail price of the processor is still relatively consistent with the previous iterations. Another thought to add to the mix would be if Intel has plans in the works to launch higher end processors based on Skylake (Kaby Lake?) in the future. The slight change in Intel's processor naming scheme (4770K to 6700K, as in 70K to 00K) also points to the potential move later in the lifetime of the product. The only hint in the naming scheme from Intel is that the 'processor numbering reflects that these processors belong to the 6th Gen Intel Core family'.

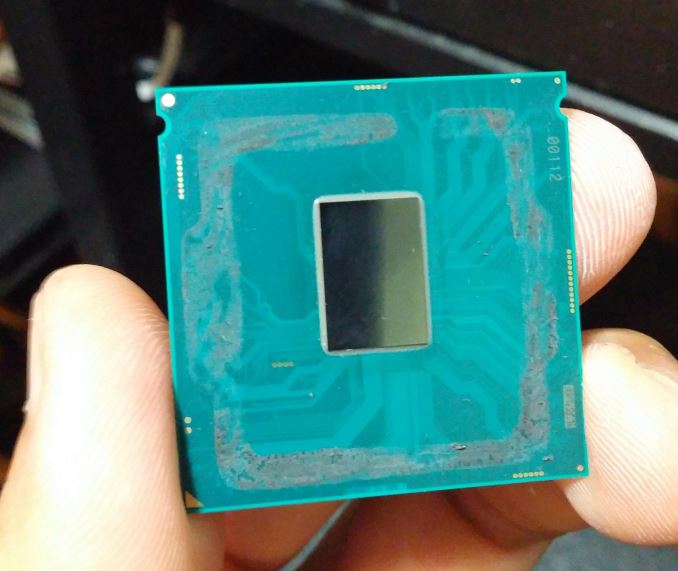

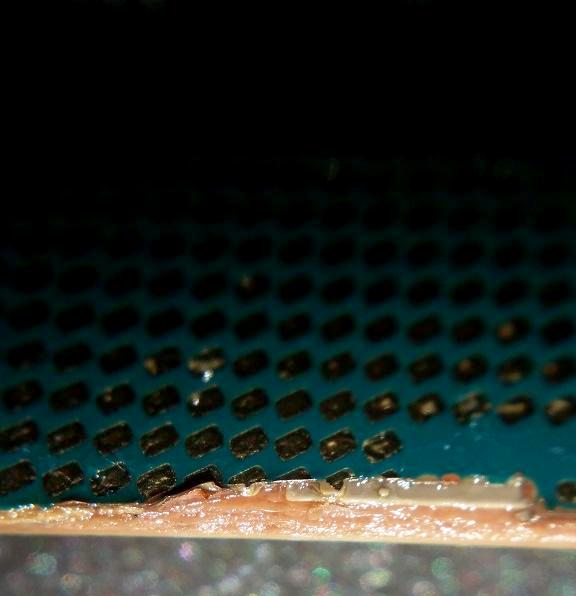

The thinness of the package has implications for removing the lid/heatspreader of the processor as well. Splave notes that previous heatspreader methods involving force, such as vices that were common during Haswell's tenure, may not be appropriate due to the thinness of Skylake. Splave shows an image of a failed attempt by another user on a Skylake CPU:

Instead, a razor method (and something warm such as a hairdryer or the bean bags that iFixit uses to warm up glue in smartphones to take them apart) to cut through the black adhesive between the package and the IHS is suggested and it what was used for the CPU above. As there are no FIVR resistors to worry about on the top of the package, the first resistance a razor blade will encounter after the black adhesive is the silicon die itself. All that being said, over at PCWatch they successfully have used a vice method.

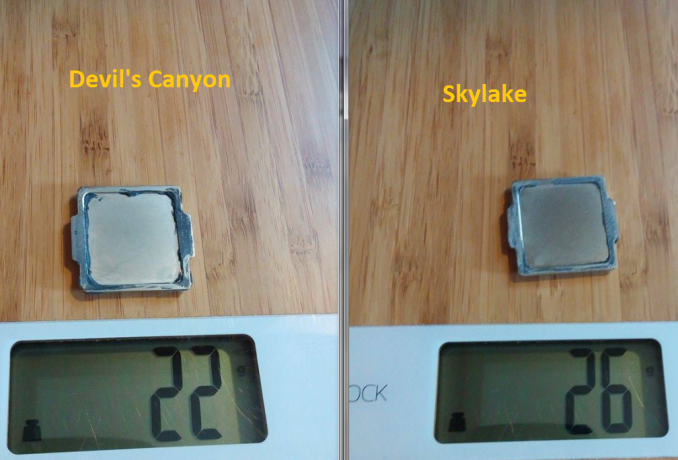

Interestingly the heatspreader for Skylake is heavier than that from Haswell by nearly 20%, moving up from 22g to 26g. Given the copper mass that usually sits on a high end processor this should not matter much, although basic aluminium coolers might see a small benefit here by virtue of the minor extra mass. This might also just be that the mounting requirements for Haswell and Skylake are the same, and the extra mass comes from the added z-height required to maintain the mounting as before.

So why are we talking about removing the heatspreader? Back with Haswell (as well as Ivy Bridge to a degree), it was discovered that the thermal interface material between the silicon die and the heatspreader was both an insufficient amount and lower quality than previous generations, as well as the heatspreader being far away from the CPU due to the black adhesive, causing more air bubbles and poorer heat transfer than is optimal. For a stock processor, this difference has little effect to the use of the system, but for overclockers it meant that they were more thermally limited than silicon limited with their overclocking.

Devil's Canyon changed that - here was a better binned Haswell processor with a higher quality package, giving a ten degrees cooler system at load. It is worth noting that previously on certain platforms Intel had been providing a mixed metal interface (generalized as a soldered interface) between the silicon and the heatspreader, which is the best but most expensive option. If the cost of the interface is reduced by 0.1 cents, then that's a significant saving on millions of processors. Devil's Canyon was a small subset of sales, so spending that extra for that specific crowd could be seen as beneficial to Intel's perspective by overclockers.

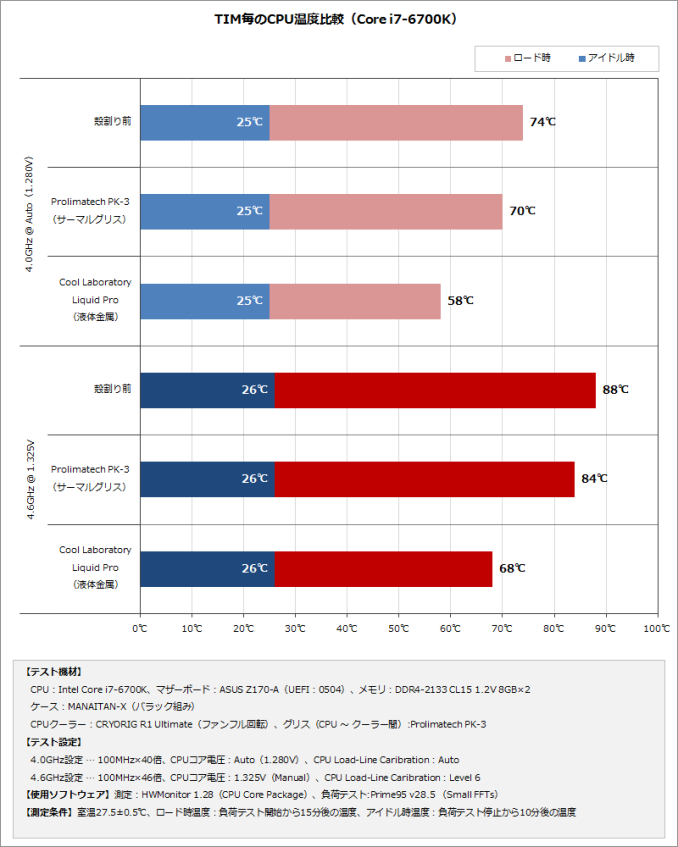

To paraphrase Splave again, he comments that the thermal paste (TIM)o n his Skylake is certainly worse than that of Devil's Canyon. If the extra mass on the IHS is coming from a taller heatspreader (by virtue of the smaller package substrate), then more TIM is needed otherwise there will be substantial air bubbling of the TIM between the CPU and the heatspreader. By replacing his own thermal paste and resecuring the heatspreader, he saw an 18°C drop in temperatures at his highest air overclock with the old paste (5.1 GHz at 1.48 volts) - from 96ºC that overheated to 78ºC on the warmest core. An 18°C drop is immense. Under those conditions, and based on rough testing not published in our Skylake review, it could equal another 100-400 MHz depending on the quality of the processor. PCWatch confirms that switching out the paste with CoolLaboratory’s Liquid Pro (a liquid metal adhesion interface) reduced temperatures at 4.6 GHz from 88ºC to 68ºC

This throws up some questions - is this just a result of design decisions for cost, or is there a Devil's Canyon type processor coming later in the design cycle?

Source: Overclock.net, PCWatch

86 Comments

View All Comments

patrickjp93 - Monday, August 10, 2015 - link

No they don't. Kaveri isn't soldered. Neither are Trinity or Richland if I remember correctly.jjj - Monday, August 10, 2015 - link

My estimate for Broadwell was that they could do a quad with no GPU at about 60mm2- we have Core M die size and some die shots for Broadwell so easier to do the math. Skyalake does seem to be bigger than expected, i'm assuming that's on the GPU side, if it was Broadwell i would have expected it to be bellow 100mm2 with the same number of EUs but we really need a die shot to be sure about what's going on.So if Zen is competitive we could finally get a lot more cores at sane prices plus cheap and fast quads. Sure the GloFo process is a bit bigger but not everything needs to go 4x for 16 cores. If they do 16 cores in 250mm2 with 70ish yiels, that's 200 good dies per wafer so maybe 50$ per chip if a wafer costs about 10k$. From 50$ their cost to 300$ in retail would be okish - Intel has it's own fabs so their costs could be half but no good way to guess their costs.However they do make some claims about how their costs scale with each nodes.

Would be hard to factor in the die size of what migrated from chipsets to the die in the last decade or so for a more accurate look at how Intel's dies are shrinking with the lack of competition but it would be interesting to plot perf and clock for clock perf, as well as retail prices and ofc include AMD.

A A10-7850K Kaveri is 245mm2 on 28nm and retails for 129$m so how much is a fair price for Skylake really?

Intel started to rip us off with Nehalem or better said Gulfy. What's the perf increase since? Maybe 2x over Nehalem depending on task? But that means clock for clock is just some 30+% gain while die size went from 263mm2 to about 60mm2 (excluding the GPU) and that doesn't even factor in what migrated from the chipset to the SoC.

PS My estimate for Broadwell was some 164mm2, derived using the Core M info available so it's likely not all that accurate but should be close enough.

bug77 - Monday, August 10, 2015 - link

Oh, you're gonna love these: http://www.hardocp.com/article/2015/08/05/intel_sk...Basically, about 10% improvement across four generations if you're doing encoding/transcoding.

Ian Cutress - Monday, August 10, 2015 - link

Somehow I don't think Dhrystone ALU, Memory Bandwidth, HyperPi or wPrime is in any way shape or form indicative of real-world encoding/transcoding. Perhaps the benchmarks we ran at AnandTech for the Skylake review would be a better initial start... :Dhttp://www.anandtech.com/show/9483/intel-skylake-r...

http://www.anandtech.com/bench/CPU/1052

Kougar - Monday, August 10, 2015 - link

I'd be more interested in what the die-size implications are for future "EP" chips. Removing 50% of that die to remove the iGP leaves an incredibly small chip. In other words an Octi-core Broadwell-E would be only a little larger than the current die size... I would hope this means consumers will finally get beefed up or higher core counts with Skylake-E.jjj - Monday, August 10, 2015 - link

There is more hope from AMD and ARM. e could get a lot more cores that just 8. AMD could go with 12-16 cores at 300$ while for ARM a quad A72 cluster with 2MB L2 is some 8mm2 so they could offer 4x the cores Intel is offering in about the same die. Remains to be seen how high A72 could clock if you give it TDP room and no HT but on the other hand no need for Intel like margins either. 125mm2 with 32 A72 cores at 150$ would be interesting but nobody is pushing ARM on desktop so we won't get that. We might get some server chips like that but with a big price premium.ViRGE - Monday, August 10, 2015 - link

You're forgetting the extra L3 cache, the additional ring buses, the extra DRAM channels, the extra PCIe lanes, and the QPI interface. There's a lot of uncore on the -E processors.extide - Monday, August 10, 2015 - link

Yeah look at the Sandy Bridge 4C/GT2 vs SnB-E 6 core (which is actually an 8 core die) -- 216 vs 435 sq mm -- so I would put 8c skylake die at about 225-250mm, although I bet they do a 10-core die, then like a 16-18 core die and then the bit 22-24 core die.extide - Monday, August 10, 2015 - link

the big* 22-24 core die, I mean.Kougar - Monday, August 10, 2015 - link

I did say larger, but not quite as much as you imply. The 6700K has 8MB L3 in this die shot already. So doubling it to an 8-core makes 16MB, very close to the 20MB in Haswell-E. So only add a little bit more space for the 4MB difference.Swapping DMI 3.0 for QPI shouldn't change much either. And for the uncore, when we double the 6700K we automatically get the quad-channel memory controllers so we aren't adding extra to make up for that. Same for the extra PCIe lanes since we'd end up with 32 of them, almost as much as Haswell-E already.

Intel would need to add very little from a straight up doubled 6700K. If I recall correctly on some of these quad chips the iGP was up to 66% of the die too...